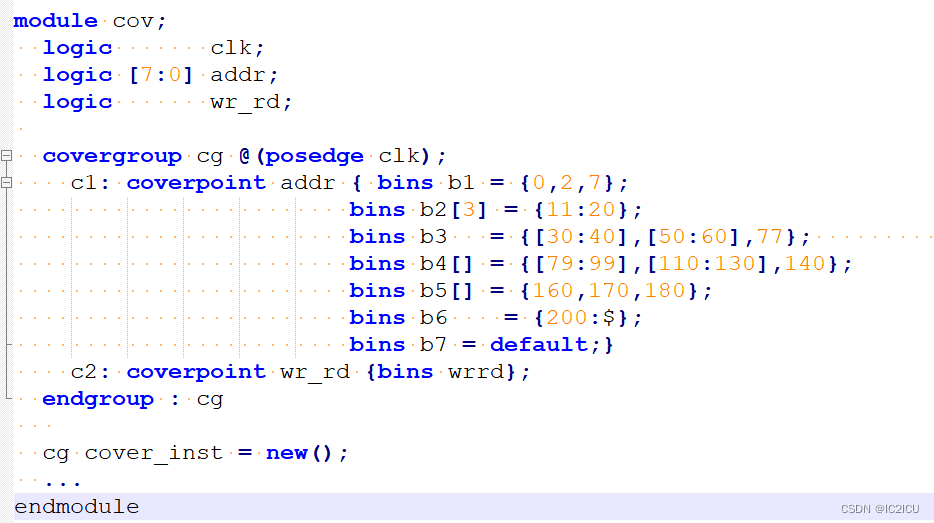

Last update images today Functional Coverage In Systemverilog

https i ytimg com vi VppesIv gR0 maxresdefault jpg - Course Systemverilog Verification 5 L13 2 Example Writing Maxresdefault https www researchgate net profile Min Zhang 109 publication 319853557 figure fig2 AS 568744491008001 1512610661372 SystemVerilog Event Regions Q640 jpg - SystemVerilog Event Regions Download Scientific Diagram SystemVerilog Event Regions Q640

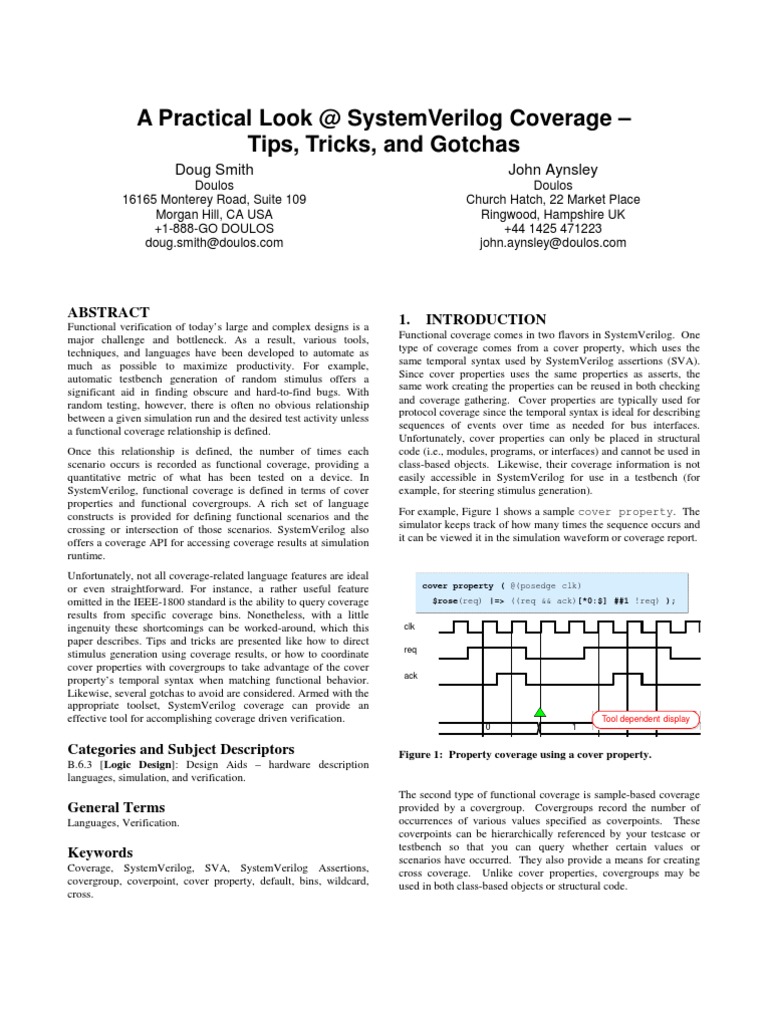

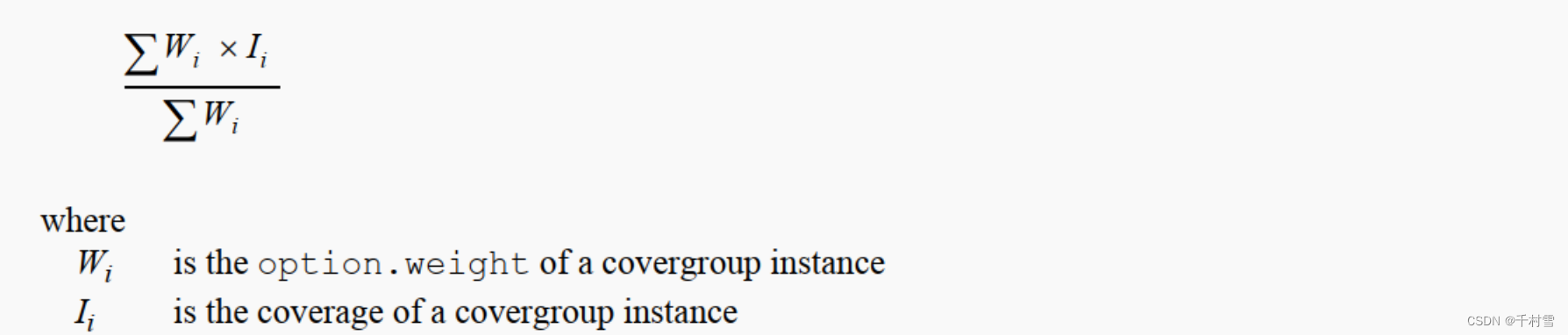

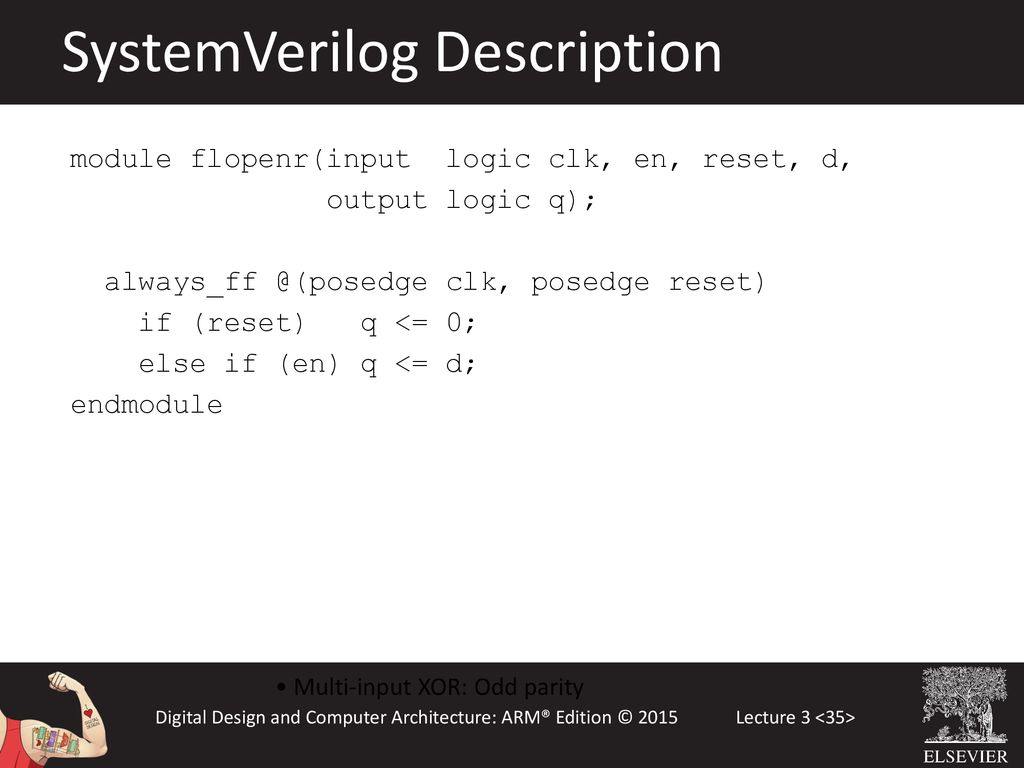

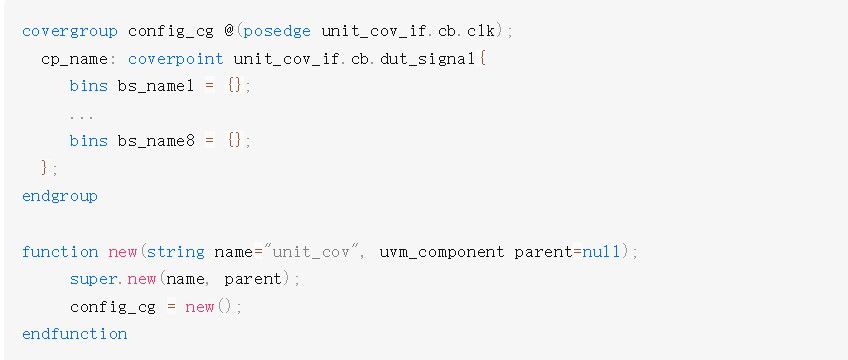

https se mathworks com help examples hdlverifier win64 xxsvdpi tsverify tsreq4 png - systemverilog coverage functional test verify mathworks generating calls system generation code set model Generating Functional Coverage In SystemVerilog From Simulink Test Xxsvdpi Tsverify Tsreq4 https img blog csdnimg cn c6e5fcc385594a0ca9f2945dc09ebe25 png - System Verilog Functional Coverage CSDN C6e5fcc385594a0ca9f2945dc09ebe25 https img blog csdnimg cn 20210322210605741 png - SystemVerilog Functional Coverage Function Coverage CSDN 20210322210605741

https i ytimg com vi XfPXQMyW4Gg maxresdefault jpg - SystemVerilog Structures YouTube Maxresdefault https ucscextension live 28cd95cf77884d15bb06 01c17c1 divio media net images systemverilog assertions and 2e16d0ba fill 2400x858 c100 jpg - SystemVerilog Assertions And Formal Verification Course UCSC Systemverilog Assertions And.2e16d0ba.fill 2400x858 C100

https habrastorage org r w1560 getpro habr upload files 411 f85 bbb 411f85bbb3d1c930a3e79b7bc0f89e4e png - Toward The January Meetup On Portable SystemVerilog Examples In Silicon 411f85bbb3d1c930a3e79b7bc0f89e4e